Memory - Segment

About

A memory segment is the division structure of the segmented memory model.

The physical address spec (physical memory) of the primary memory is divide by segment. See addressing

This article is about a physical segment but the virtual memory implements also virtual segment ????

Articles Related

Addressing

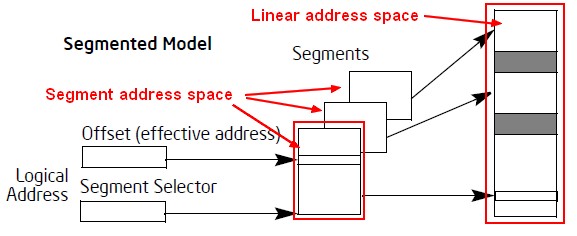

To address a byte in a segment, a program issues a logical address that maps to a linear address.

Internally, all the segments that are defined for a system are mapped into the processor’s linear address space.

To access a memory location, the processor translates transparently each logical address into a linear address.

Usage

Reliability

The primary reason for using segmented memory is to increase the reliability of programs and systems. For example, placing a program’s stack in a separate segment prevents the stack from growing into the code or data space and overwriting instructions or data, respectively.

Code, data, and stacks are therefore typically contained in separate segments. and a program will have many independent address spaces (one segment).

A program may have many independent of them to keep the type of data separate:

- data (data tables). See Assembly - Data Section (DS)

- and stack

Then :

- Code addresses would always refer to the code space,

- Stack addresses would always refer to the stack space.

- data addresses would always refer to the data space.

See type

Shared Memory

Certain segments may even be shared between programs. See: shared memory

Management

Selector

A segment selector is the unique identifier of a segment and is used in the first part of logical address. See Memory Segment - Segment Selector

Register

Type

As in a segmented model, the memory is split, the type of bit that they contains is different and it permits to increase reliability. See reliability

Number

Programs running on an IA-32 processor can address up to 16,383 segments of different:

- and types.

Size

On IA-32 processor, each segment can be as large as 232 bytes.

Address space

A segment creates an address spaces that is addressable.

Internally, all the segments are mapped into the processor’s linear address space.